Dear friends,

I already added SPDIF-outputs to secend gen. CD-Players:

CX23035-SPDIF Out

No I would like to add it to the CDP-101, one of the very first CD-Players.

Mine is in mint condition and ran for about 200hours. I bought it first hand from a dealer in 2014

who stored 3 units for about 30 years.

The big problem:

Digital outputs ICs like the DIT4192 or WM8805 work with "fs" (Frames I guess) that are based on multiples of a 4.2336MHz clock.

As one example, a clock of 16.9344MHz (four times of 4.2336MHz) generates 384fs.

99% of the CD-Players sold are based on the multiples of 4.2336MHz.

In the link above, the player works with a clock of 8.4672MHz, which is the exact half of 16.9344MHz.

Both clocks can be easily synced and the DIT4192 grabs it´s 384fs from the 192fs source.

Works perfectly for more than a decade.

But the Sony CDP-101 is an exception. It runs on 8.6436MHz, which equals 196 fs, a ratio of 1,959183673469388 to 16.9344MHz

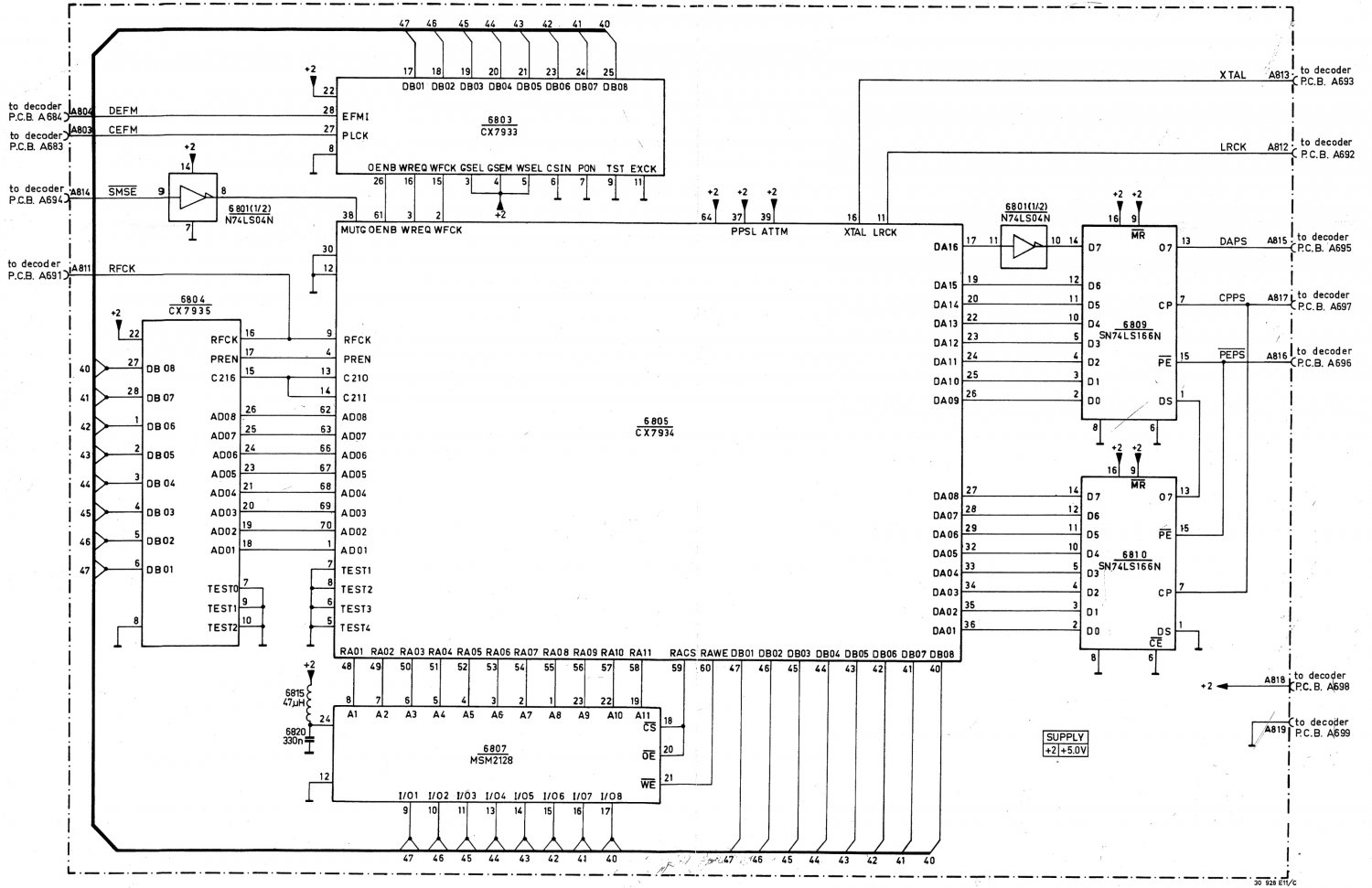

Reason is the RAM/Decoder IC CX7934.

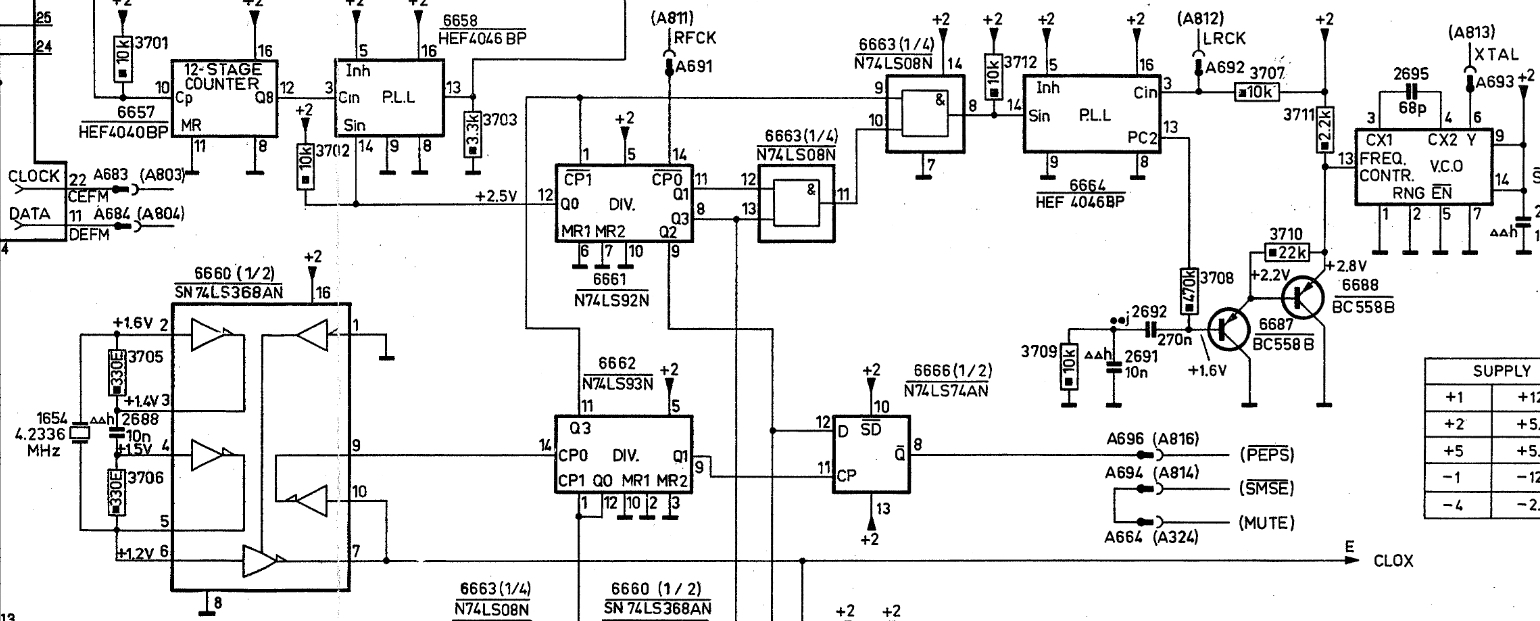

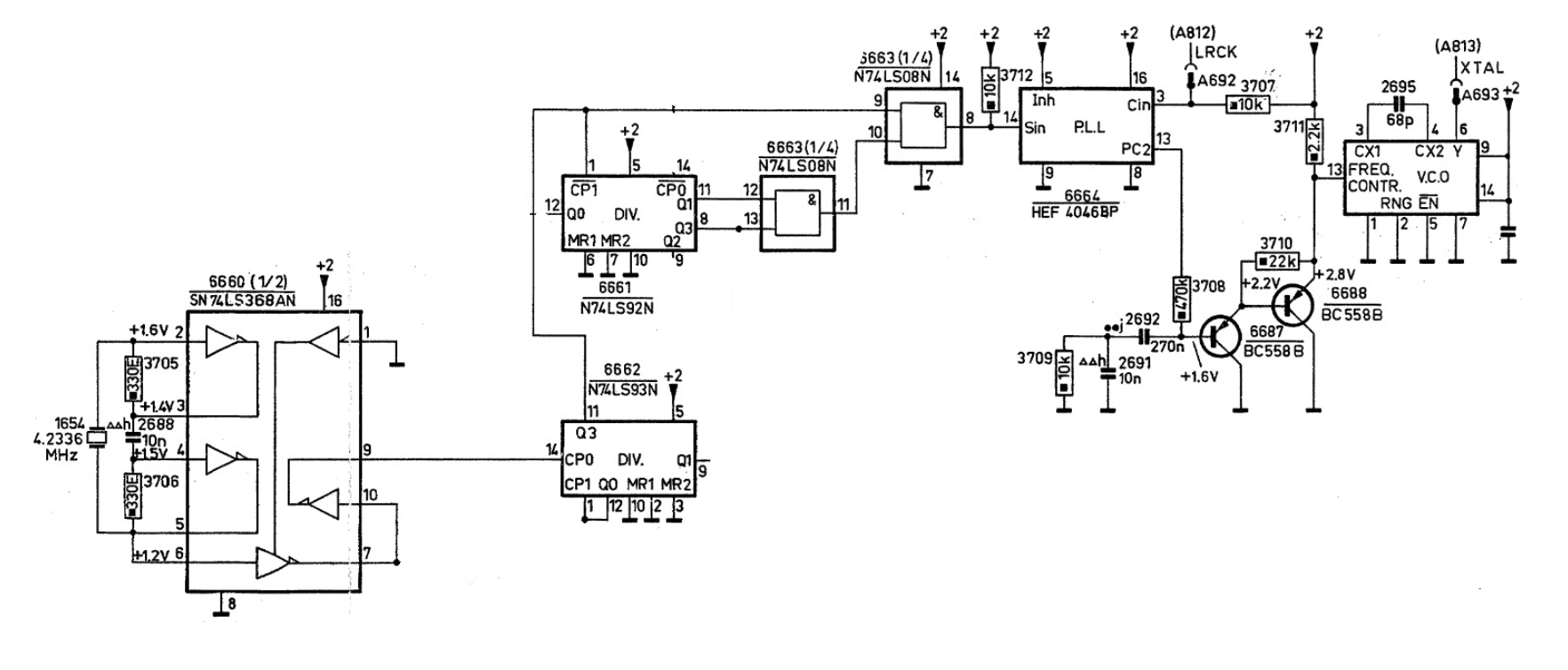

40 years ago, this schematics are from September 1983, Philips had the same problem: They used the CX7934 IC from Sony in the CD-200 and CD-300, but ran the rest of the already on 4.2336MHz:

So they built a PLL. To my understanding, A813 on the far right sends 8.6436MHz to the CX7934, which emits the LR-Clock of 44.1kHz over A812 back to the PLL, where it is synced with

So they built a PLL. To my understanding, A813 on the far right sends 8.6436MHz to the CX7934, which emits the LR-Clock of 44.1kHz over A812 back to the PLL, where it is synced with

the 44.1KHz derived from a 4.2336MHZ base:

The IC on the far right is SN74LS624N. The only IC that is obsolete, but I bought one. All other IC are still available. Here is the same schematics cleaned up:

So I could rebuilt it, using a 16.9344MHz external clock that also provides 4.2336MHz, replacing IC 6660 on the left.

But this circuit must be very jittery! Any advises to claean up the jitter or for trying a different approach?

The easiest solution could be a SPDIF transmitter that does not need a master clock and generates it from the Bitclock and L/R Clock,

but to my knowledge, such transmitters do not exist.

Another approach might be to sync the Sony CDP-101 master clock 8.6436 to 16.9344MHz.

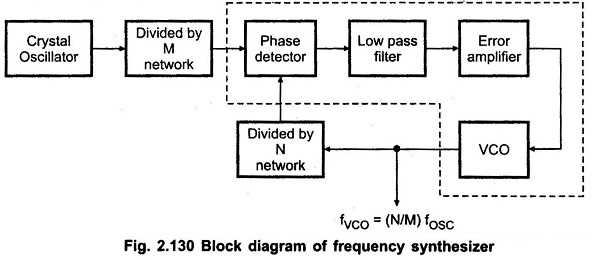

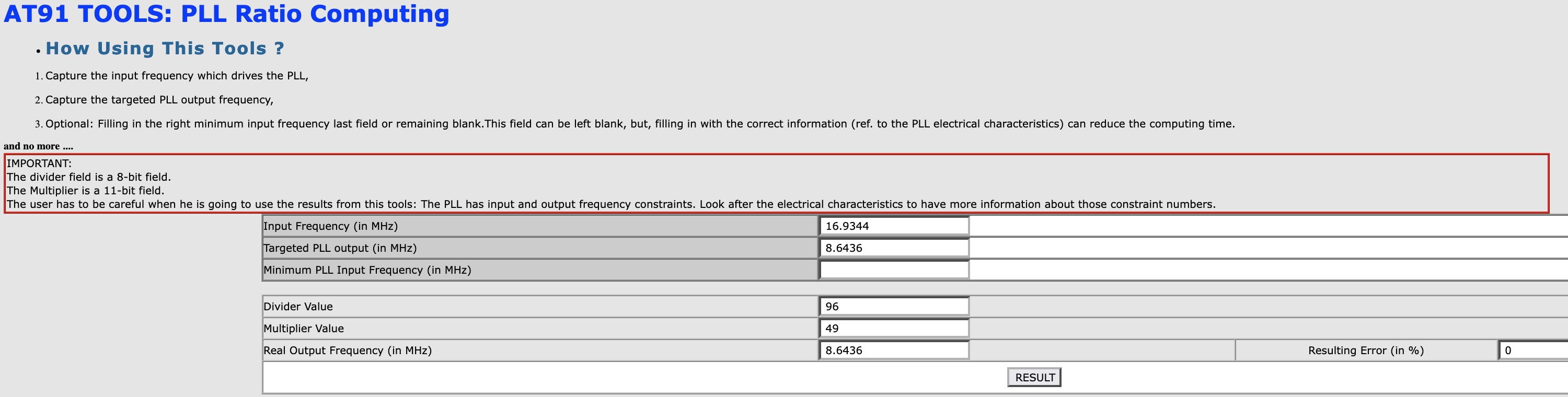

Division-multiplication would look like this:

So, any advice on the matter?

BTW, data sent from the CX7934 is the same as the later CX23035: 16-Bit Right-Justified, twos complement, MSB first.

All the best, Herbert

I already added SPDIF-outputs to secend gen. CD-Players:

CX23035-SPDIF Out

No I would like to add it to the CDP-101, one of the very first CD-Players.

Mine is in mint condition and ran for about 200hours. I bought it first hand from a dealer in 2014

who stored 3 units for about 30 years.

The big problem:

Digital outputs ICs like the DIT4192 or WM8805 work with "fs" (Frames I guess) that are based on multiples of a 4.2336MHz clock.

As one example, a clock of 16.9344MHz (four times of 4.2336MHz) generates 384fs.

99% of the CD-Players sold are based on the multiples of 4.2336MHz.

In the link above, the player works with a clock of 8.4672MHz, which is the exact half of 16.9344MHz.

Both clocks can be easily synced and the DIT4192 grabs it´s 384fs from the 192fs source.

Works perfectly for more than a decade.

But the Sony CDP-101 is an exception. It runs on 8.6436MHz, which equals 196 fs, a ratio of 1,959183673469388 to 16.9344MHz

Reason is the RAM/Decoder IC CX7934.

40 years ago, this schematics are from September 1983, Philips had the same problem: They used the CX7934 IC from Sony in the CD-200 and CD-300, but ran the rest of the already on 4.2336MHz:

the 44.1KHz derived from a 4.2336MHZ base:

The IC on the far right is SN74LS624N. The only IC that is obsolete, but I bought one. All other IC are still available. Here is the same schematics cleaned up:

So I could rebuilt it, using a 16.9344MHz external clock that also provides 4.2336MHz, replacing IC 6660 on the left.

But this circuit must be very jittery! Any advises to claean up the jitter or for trying a different approach?

The easiest solution could be a SPDIF transmitter that does not need a master clock and generates it from the Bitclock and L/R Clock,

but to my knowledge, such transmitters do not exist.

Another approach might be to sync the Sony CDP-101 master clock 8.6436 to 16.9344MHz.

Division-multiplication would look like this:

So, any advice on the matter?

BTW, data sent from the CX7934 is the same as the later CX23035: 16-Bit Right-Justified, twos complement, MSB first.

All the best, Herbert

Last edited: