Sorry for leaving you hanging with this for so long. Some of these days I don't get much done besides watching YouTube and listening to music...

#DepressionSux

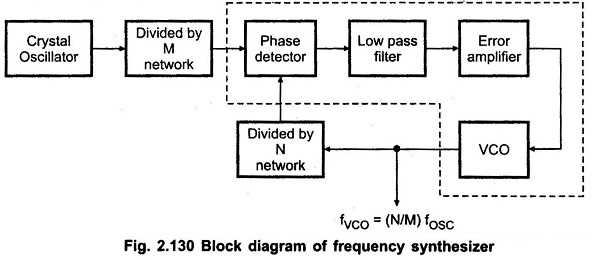

Anywho, this problem can fundamentally be tackled in both directions, depending on your priorities. The circuitry required would be almost the same either way, just differing in which divider goes where and the reference clock. It is pretty much a textbook integer-N PLL synthesizer.

(

from here)

If you want to synthesize 8.6436 MHz but not have an undue jitter penalty, the trick is using the phenomenon of

injection locking to pull the reference xtal oscillator. The downside of this being that some experimentation with levels and coupling may be required, but I'd start with

a whole lotta nothing for coupling capacitance, maybe 3-5 pF. You just want PLL output to nudge the crystal oscillator on the right frequency reliably, not swamp the input and impose all the PLL phase noise onto it. An advantage of this approach is that you can just turn off power to your PLL if you want and use the player pretty much stock.

The alternative would be using an extra VCXO instead of the typical integrated CMOS VCO. But try finding an 8.6436 MHz crystal these days... (Plan B, convert the onboard XO into a VCXO. It's a bit of an odd topology so not sure how easy that would be.)

Now 16.9344 MHz / 8.6436 MHz is a ratio of 96 / 49, so you'd need an N divider of 49 and an M divider of 96.

96 = 3 * 2 * 2 * 2 * 2 * 2 or 12 * 8, so this is why a 74xx92 divide-by-12 counter (/2 + /6) and a 74xx93 4-bit binary counter (/2 + /8) come in handy.

The ANDing of 6LRCK, 6LRCK/2 and 6LRCK/6 done by Philips results in only one logic high pulse every 12 counts or 6 whole 6LRCK periods if you look at the '92 truth tables. (Not exactly sure why they found that preferable for phase detector input over piping in 6LRCK/6 straight away, but I haven't looked at the peculiarities of 4046 phase detectors in many years either.)

Either way, dividing all the way down to LRCK (i.e. 44.1 kHz) for your PLL when it could also be running at 176.4 kHz is not ideal in terms of phase noise, which is probably what that guy was getting at. And that's in addition to the general phase noise penalty if you were to replace the reference oscillator with PLL output altogether. (CMOS VCOs tend not to be phase noise kings even when they do have a nice clean supply voltage, their Q is just too low and they have a large pulling range.)

49 = 7 * 7 is a bit of a pig. That would probably take two 74xx90 decade counters in bi-quinary mode with an external AND to reset them once Qa and Qc (Q0 and Q2) go high so they don't count past 6. I'll have to consult my textbooks on whether that's correct, pretty sure I've seen something on the topic in there somewhere. (I'm not a logic guru by any means.) But that's one for tomorrow.

In case of the Philips player, the CX7934 is doing the dirty work with its LRCK output. So that's why they went with that as their PLL reference frequency, I guess.