-

WANTED: Happy members who like to discuss audio and other topics related to our interest. Desire to learn and share knowledge of science required. There are many reviews of audio hardware and expert members to help answer your questions. Click here to have your audio equipment measured for free!

- Forums

- Audio, Audio, Audio!

- DACs, Streamers, Servers, Players, Audio Interface

- Digital To Analog (DAC) Reviews and Discussion

You are using an out of date browser. It may not display this or other websites correctly.

You should upgrade or use an alternative browser.

You should upgrade or use an alternative browser.

ESS THD ‘Hump’ Investigation

- Thread starter jackenhack

- Start date

- Thread Starter

- #82

the hump is IMD not thd, for christ's sake

It's both.

dc655321

Major Contributor

- Joined

- Mar 4, 2018

- Messages

- 1,597

- Likes

- 2,236

D

Deleted member 65

Guest

the hump is IMD not thd, for christ's sake

@jackenhack is correct, browse back a couple of pages and you'll see christ's (amir) post.

IMD and HD are mathematically related; a given level of one produces a fixed level of the other. Basic (but messy) math (trigonometry). Because the analyzer plots THD and not just the HD terms it may obfuscate the relationship but it is there...

- Thread Starter

- #87

Well, I managed to kill the DAC chip on my board by misadventure. So I have to order a new board when I get the money to do so. Christmas has put a dent in my wallet. I'll keep you guys updated.

- Thread Starter

- #88

Kind of explains why I had problems communicating with the DAC.

Shame it happened. You were doing really good work there.

- Thread Starter

- #90

We now know that the I2C bus is not 5 volts tolerant anyway!

Ouch!

We now know that the I2C bus is not 5 volts tolerant anyway!

That's odd...5th page of the datasheet straight up lists the I2C clock and serial I/O pins as amongst of the 5v tolerant ones...

wadec22

Senior Member

- Joined

- Oct 9, 2018

- Messages

- 319

- Likes

- 242

The painful sound of ESS dac is only audible for the guys with 'golden ears' who can hear THD under -60db on their reference music and has headphones with lower THD than Toppings DAC.

I'm still learning so this is an honest comment/question.

On the noise test files from the test thread, most folks are hearing noise at -70db at normal listening volume. I was able to hear -90db by cranking the volume (barely).

Wouldn't we want noise to be at least -85 or -90 to have peace of mind?

Are these two threads not related due to the type of distortion being measured?

I've decided to avoid sabre DACs for now to avoid the hump. I can't afford the units that don't have it. I have the M10 and RME ADI2. Budget wise, I'd go El DAC.

Probably overreaction on my part I'm sure.

Cranking the volume is only reasonable if you listen at that level. The idea is to figure out what noise floor is acceptable to you at normal listening levels. Room noise (far) dominates the noise for most of us.

The ESS "hump" is inaudible in normal (or even very loud) listening IMO.

You can pay a lot for "peace of mind" -- witness the multi-thousand dollar cable sales to provide peace of mind for those that (think they) can hear every atom out of place... The problem is letting others convince you what is required for your own peace of mind. That is called Marketing.

All IMO! - Don

The ESS "hump" is inaudible in normal (or even very loud) listening IMO.

You can pay a lot for "peace of mind" -- witness the multi-thousand dollar cable sales to provide peace of mind for those that (think they) can hear every atom out of place... The problem is letting others convince you what is required for your own peace of mind. That is called Marketing.

All IMO! - Don

wadec22

Senior Member

- Joined

- Oct 9, 2018

- Messages

- 319

- Likes

- 242

Cranking the volume is only reasonable if you listen at that level. The idea is to figure out what noise floor is acceptable to you at normal listening levels. Room noise (far) dominates the noise for most of us.

The ESS "hump" is inaudible in normal (or even very loud) listening IMO.

You can pay a lot for "peace of mind" -- witness the multi-thousand dollar cable sales to provide peace of mind for those that (think they) can hear every atom out of place... The problem is letting others convince you what is required for your own peace of mind. That is called Marketing.

All IMO! - Don

I agree with a lot of that but as a hobbyist even, I simply prefer to avoid it. If you believe the gentleman from Benchmark, it is a symptom of incorrect DAC implementation.

Like I said, I realize my perspective is probably overreaction buy if you can avoid it with a budget unit like the El DAC, then why not... I don't think you have to pay extra to avoid it.

All preference of course. I'm certainly not claiming I can hear the thing, which fuels your point.

I would even probably live with it if a unit I liked had aesthetics and features I wanted that I couldn't get elsewhere.

I'm still learning so this is an honest comment/question.

On the noise test files from the test thread, most folks are hearing noise at -70db at normal listening volume. I was able to hear -90db by cranking the volume (barely).

Wouldn't we want noise to be at least -85 or -90 to have peace of mind?

[...]

You need not to increase the volume to huge levels, just to the a high but still comfortable listening level to your ears.

I was unable to hear the 2nd harmonic, nor the 3rd one on -60dB for 1KHz sinewave. On headphones I couldn't hear the 4th and 5th harmonics either, but when using monitors speakers I was able to hear both.

So harmonics are more difficult to perceive with our ears than the background noise.

*Notice: DWA is Data-Weighted Averaging and DEM is Dynamic Element Matching. Although DWA is the most widely used DEM algorithm, these are different thing. I misused the term DWA and I fixed them properly. I apologise for making confusion.

I found this article about new ESS dac. And it starts with "As per Mark Mallinson," which means that it is based on the statement of former Operations Director for ESS Technology.

https://6moons.com/audioreviews2/resonessence/2.html

According to the article, it is Pro and non-Pro version that discriminates ESS dac with/without hump. So Benchmark dac with es9028pro has no hump, and Khadas tone board with es9038q2m has hump.

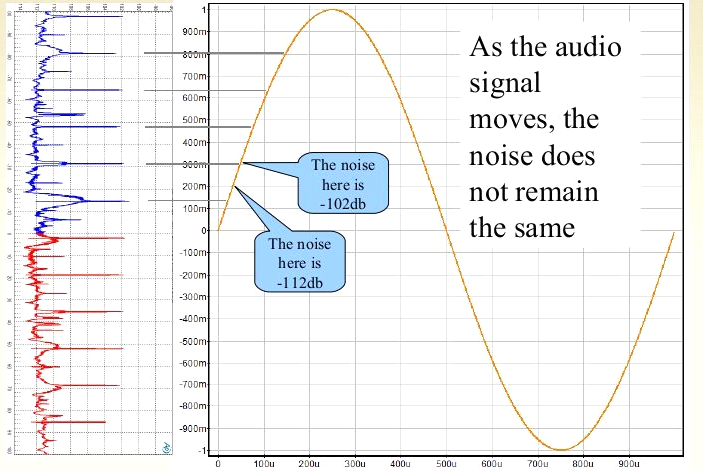

This is Noise vs Input level measurement, not IMD measurement. But according to audio precision, "The SMPTE IMD measurement includes noise within the passband." So the rise of noise can also effect SMPTE/DIN IMD measurement of Amirm.

And I was right about expecting DEM to be the cause of THD hump of ESS dac.

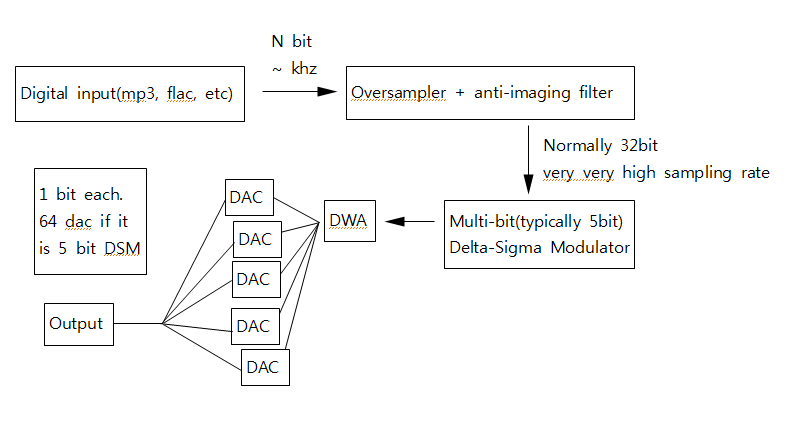

To simply explain DWA, it is implemented as a circuit that randomly allocates the output signal of delta-sigma modulator to individual 1-bit dac to hide the switching noise and distortion by element mismatch of each dac. But the randomizing algorithm should be designed very carefully in order to maximize its performance.

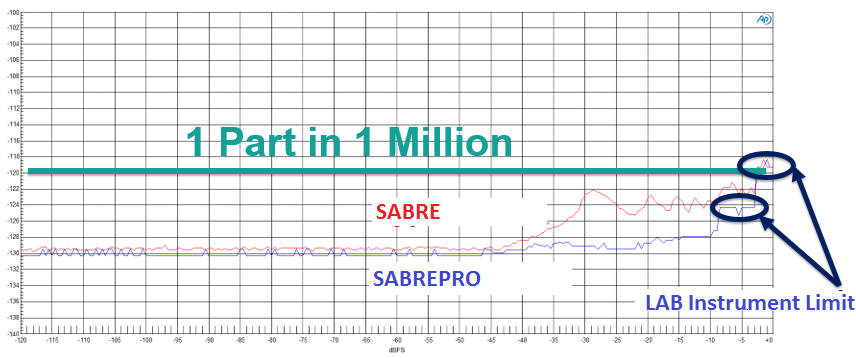

"This one is a bit complex but a long-standing overlooked potential improvement. It's complex mathematically but relates to 'mapping' the digital signals to analog elements on the chip. The improvement can be seen on lab instrumentation. Both Sabre and Sabre Pro are very very good and better than 1 part in a million.

But what about that bump at -30dB? In the Pro it is now absent to exhibit a predictable noise vs signal level shape. Whilst we have no evidence that this is audible, it is fixed now."

'Mapping the digital signals to analog element' part is definitely DWA part. I suspect that he tried to explain US 8,984,035 B2 patent because it is about the method of scrambling bit allocation of dac on the output.(but I'm not so sure about this because I'm not an engineer so I can misunderstand the content of the patent.)

https://patentimages.storage.googleapis.com/f0/08/cc/0b71c8764107ee/US8984035.pdf

And furthermore, it seems that the difference between hyperstream and hyperstream II is improved algorithm that controls the noise of dac.

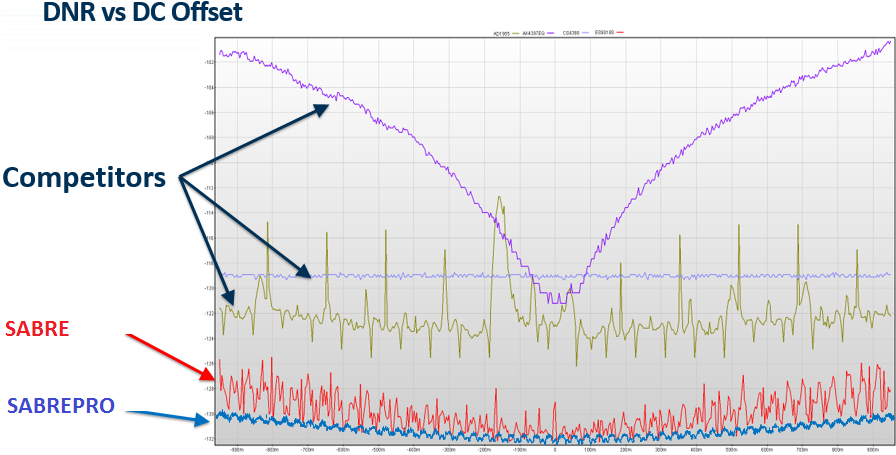

As a result, they have managed to suppress the noise of their dac and it shows well on the graph. This graph is measurement of Dynamic range on y axis, and DC level on x axis. The following picture describes it well.

Source: https://www.yumpu.com/en/document/read/23182504/noise-shaping-sigma-delta-dacs-ess-technology-inc

So we can predict the relationship between dynamic range and input level or frequency from this graph. And we can also predict that the hump seems to be because of the noise level rising on each end of DC level.

It is a sad thing that usually we can't get this measurement on most dac chip. Only Cirrus logic advertises their effort to deal with this issue.(The blue line on the graph above is cs4398. And they had released a white paper boasting their DEM design on here) But Texas Instrument and Asahi Kasei also have their own ways to deal with it too.

To conclude, the hump is made by a flaw of hyperstream modulator(although it's still better than old competitors), but it is fixed on PRO lineup.

I found this article about new ESS dac. And it starts with "As per Mark Mallinson," which means that it is based on the statement of former Operations Director for ESS Technology.

https://6moons.com/audioreviews2/resonessence/2.html

According to the article, it is Pro and non-Pro version that discriminates ESS dac with/without hump. So Benchmark dac with es9028pro has no hump, and Khadas tone board with es9038q2m has hump.

This is Noise vs Input level measurement, not IMD measurement. But according to audio precision, "The SMPTE IMD measurement includes noise within the passband." So the rise of noise can also effect SMPTE/DIN IMD measurement of Amirm.

And I was right about expecting DEM to be the cause of THD hump of ESS dac.

To simply explain DWA, it is implemented as a circuit that randomly allocates the output signal of delta-sigma modulator to individual 1-bit dac to hide the switching noise and distortion by element mismatch of each dac. But the randomizing algorithm should be designed very carefully in order to maximize its performance.

"This one is a bit complex but a long-standing overlooked potential improvement. It's complex mathematically but relates to 'mapping' the digital signals to analog elements on the chip. The improvement can be seen on lab instrumentation. Both Sabre and Sabre Pro are very very good and better than 1 part in a million.

But what about that bump at -30dB? In the Pro it is now absent to exhibit a predictable noise vs signal level shape. Whilst we have no evidence that this is audible, it is fixed now."

'Mapping the digital signals to analog element' part is definitely DWA part. I suspect that he tried to explain US 8,984,035 B2 patent because it is about the method of scrambling bit allocation of dac on the output.(but I'm not so sure about this because I'm not an engineer so I can misunderstand the content of the patent.)

https://patentimages.storage.googleapis.com/f0/08/cc/0b71c8764107ee/US8984035.pdf

And furthermore, it seems that the difference between hyperstream and hyperstream II is improved algorithm that controls the noise of dac.

As a result, they have managed to suppress the noise of their dac and it shows well on the graph. This graph is measurement of Dynamic range on y axis, and DC level on x axis. The following picture describes it well.

Source: https://www.yumpu.com/en/document/read/23182504/noise-shaping-sigma-delta-dacs-ess-technology-inc

So we can predict the relationship between dynamic range and input level or frequency from this graph. And we can also predict that the hump seems to be because of the noise level rising on each end of DC level.

It is a sad thing that usually we can't get this measurement on most dac chip. Only Cirrus logic advertises their effort to deal with this issue.(The blue line on the graph above is cs4398. And they had released a white paper boasting their DEM design on here) But Texas Instrument and Asahi Kasei also have their own ways to deal with it too.

To conclude, the hump is made by a flaw of hyperstream modulator(although it's still better than old competitors), but it is fixed on PRO lineup.

Last edited:

- Thread Starter

- #99

That's odd...5th page of the datasheet straight up lists the I2C clock and serial I/O pins as amongst of the 5v tolerant ones...

Well, to be precise I added 3.3 Volts to a 3.3 Volt rail by mistake, so it’s 6.6 Volts.

- Thread Starter

- #100

jackenhack, try to send your board for a repair. the DAC chip should be easily replaceable with proper tools.

I have a reflow oven and heat gun; the problem is to get hold of the DAC. It's available at Alibaba, but only in quantities of ten.

Similar threads

- Replies

- 45

- Views

- 4K

- Poll

- Replies

- 303

- Views

- 46K

- Replies

- 1

- Views

- 410

- Replies

- 378

- Views

- 96K

- Poll

- Replies

- 47

- Views

- 13K