Maybe not put in a random value

How big is the offset?

How big is the offset?

The offset is 26.8 mV. If you appythe formula, you get a value that in binary is more than 16 bits, that's why I ended up trying random values.

I have no clue. And what surprises me more is that it is not symmetrical. Channels 2468 read 0.0 mV. Both sides Ged fed by the same analogue power line and there is nothing else connected to it nor any other component anywhere close. The schematic is quite simple actually.Or it’s higher than you can compensate for… the question is, where does it come from?

Thanks! Will test that.Nice to have results!

For the DC offset I would check if pin 7 and 24 have exactly equal resistances to the ground plane, same for 12 and 19.

Further look for equal voltages on 10 and 21.

Tempting to try the DC-offset registers if nothing else works. Maybe it is a normal problem to have with this chip? I have never seen this in other DACs, but these have always been current outputs.

maybe a bad capacitor (leaky) on the GSN_L? Try desoldering them perhaps?I have no clue. And what surprises me more is that it is not symmetrical. Channels 2468 read 0.0 mV. Both sides Ged fed by the same analogue power line and there is nothing else connected to it nor any other component anywhere close. The schematic is quite simple actually.

desoldering

voltages in pins 10 and 21 identical 3.297VNice to have results!

For the DC offset I would check if pin 7 and 24 have exactly equal resistances to the ground plane, same for 12 and 19.

Further look for equal voltages on 10 and 21.

Tempting to try the DC-offset registers if nothing else works. Maybe it is a normal problem to have with this chip? I have never seen this in other DACs, but these have always been current outputs.

thanks, i still think it might be the ADC i use to capture the signal is DC decoupled, but don't know...Congratulations! Looks like it is working fine now.

not really, other than changing the only component that is external to the DAC chip that is different for one group of channels vs the other. btw, i just desoldered the 4 1uF caps that go to pins 10 11 20 and 21 and measured them. the only value out of the normal was on cap to pin 11, that was 1.57 uF. Changed caps to pins 10 and 11 for others "borrowed" from another PCB. The 26 mV are still thereAny reason for the cap substitution?

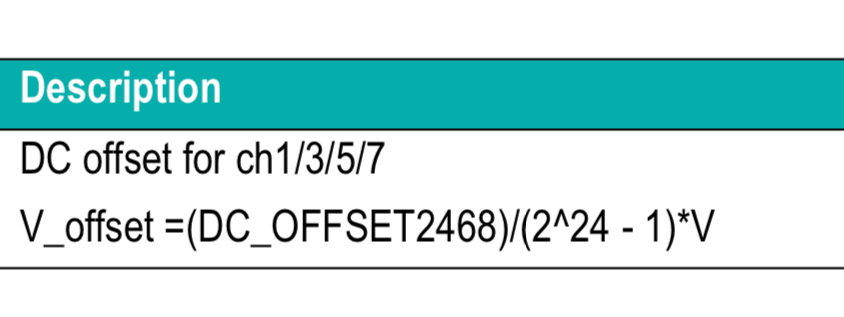

I am 99% sure the formula in the datasheet is wrong. This is what the datasheet says:On another topic; the DC offset value had to be stored in 2 registers. Never got this to work for the signed double THD compensation in the ES9038pro. I simply split the double in a high and a low nible. Even tiny compensations (e.g. -10) had extreme results on the THD.

thanks!I agree that your calculation is more likely.

My problem is how to distribute 16 bits over 2 8 bit registers. Which bits go first (LSB should go in the first register, MSBs in the second according to little endian) but never got it to work in my arduino code. Any ideas on why?

E1DA has an app that can do this for their DAC, very nice interface. See

Datasheet indeed says LSB first. How do you do it in code?I agree that your calculation is more likely.

My problem is how to distribute 16 bits over 2 8 bit registers. Which bits go first (LSB should go in the first register, MSBs in the second according to little endian) but never got it to work in my arduino code. Any ideas on why?

LSB first. But I think the problem is in splitting the 16 bits into 2 times 8 bits. I use int16 and int8 for this in c++, maybe this does not work well with lowbyte and highbyte function.Datasheet indeed says LSB first. How do you do it in code?

The int is whatever the CPU uses. The endianness is undefined in C(++). Better do the splitting yourself:LSB first. But I think the problem is in splitting the 16 bits into 2 times 8 bits. I use int16 and int8 for this in c++, maybe this does not work well with lowbyte and highbyte function.

Thanks! I'll try that. Have to dig up the code from somewhere on my pcThe int is whatever the CPU uses. The endianness is undefined in C(++). Better do the splitting yourself:

LSB = value & 0xff

MSB = value >> 8