- Joined

- Nov 23, 2020

- Messages

- 182

- Likes

- 130

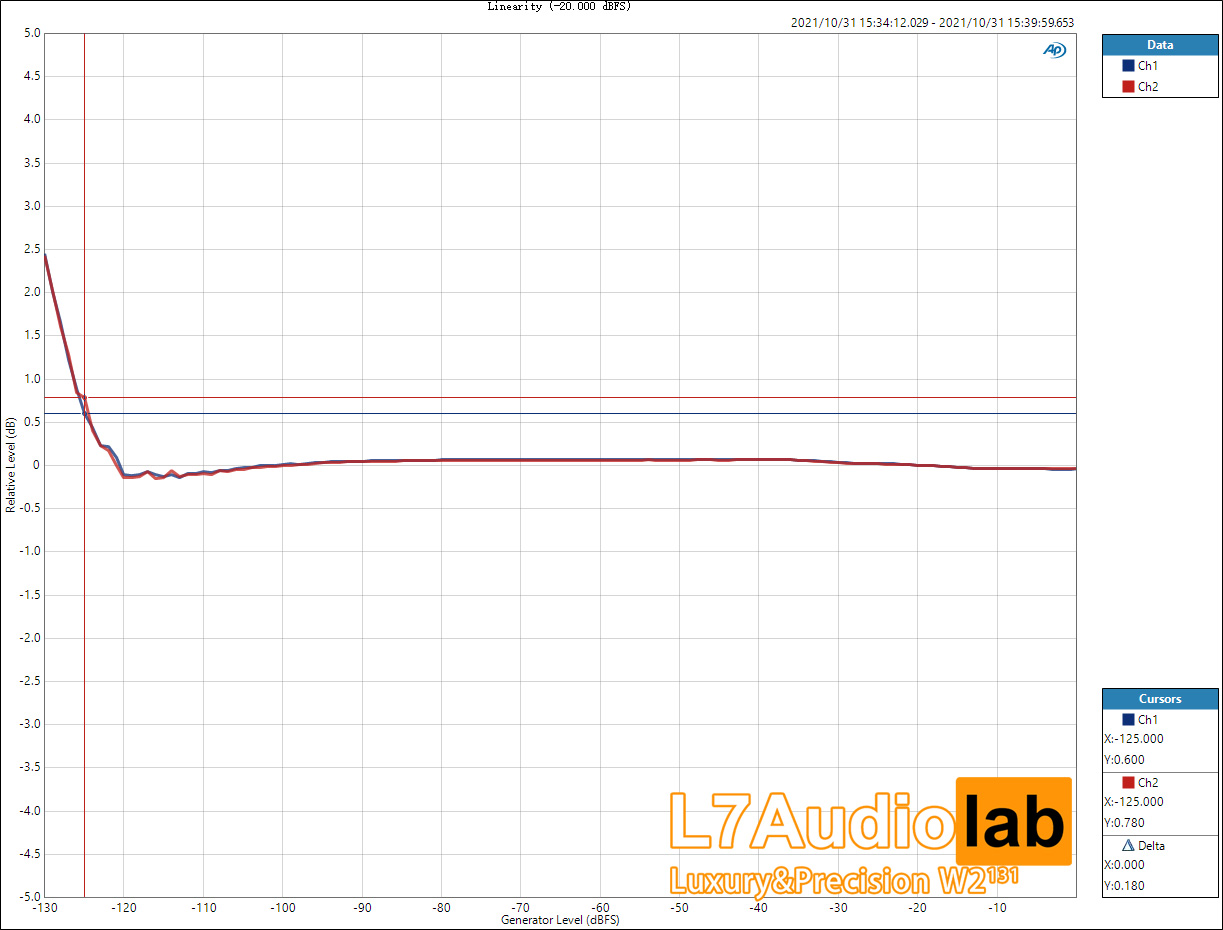

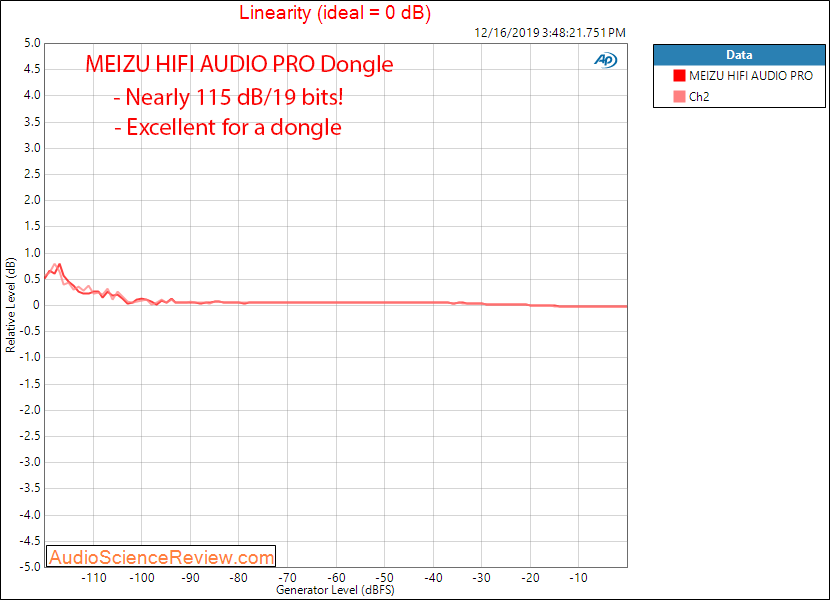

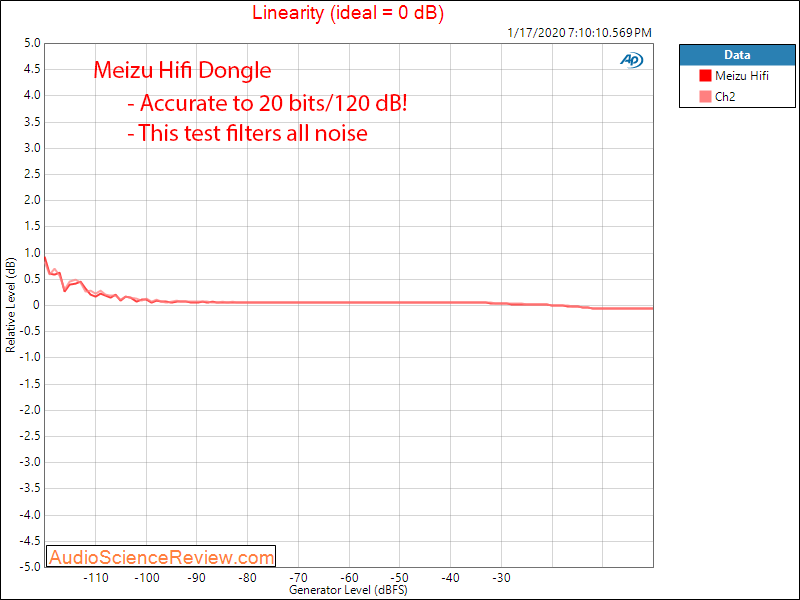

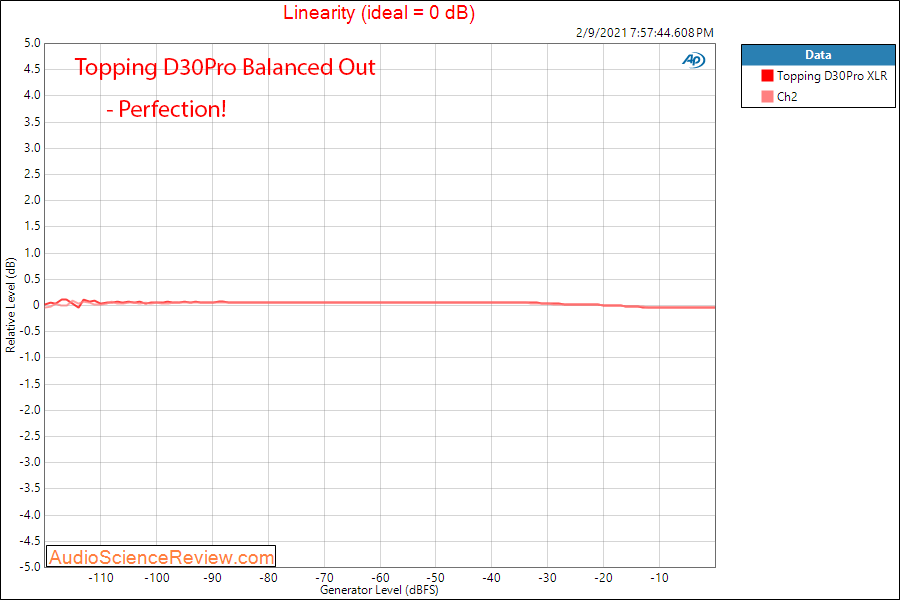

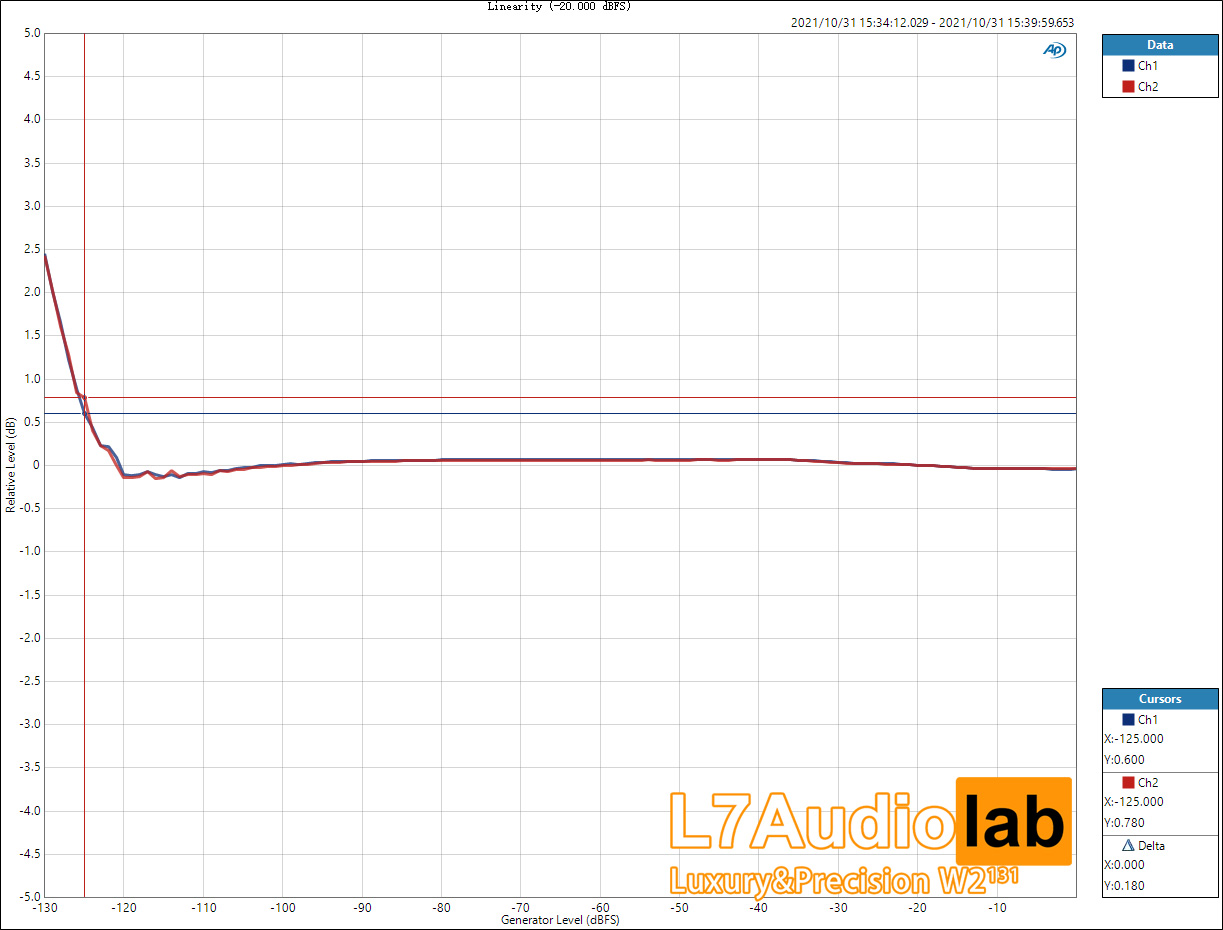

Does anyone know what causes the slight wobble in linearity from Cirrus chips above -35dBfs?

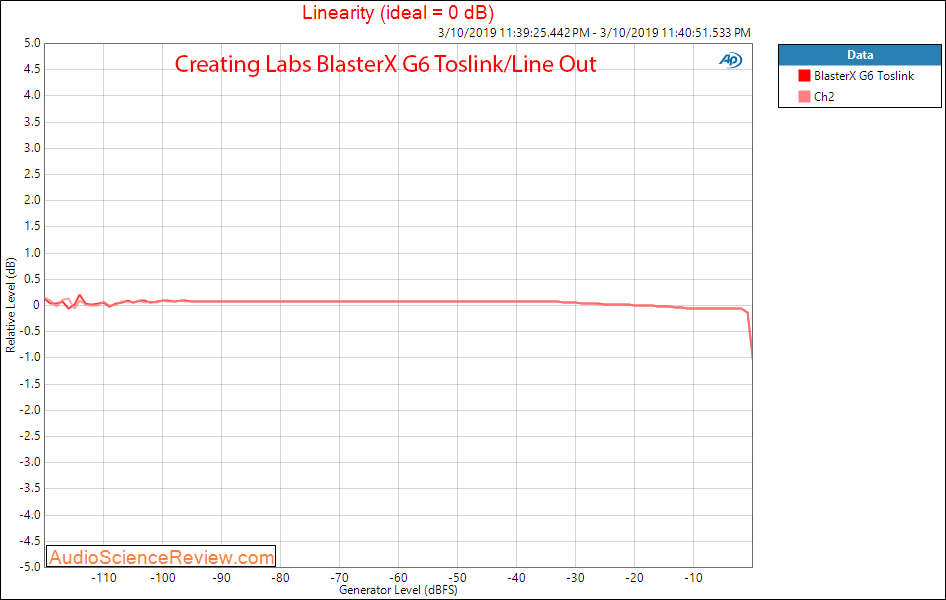

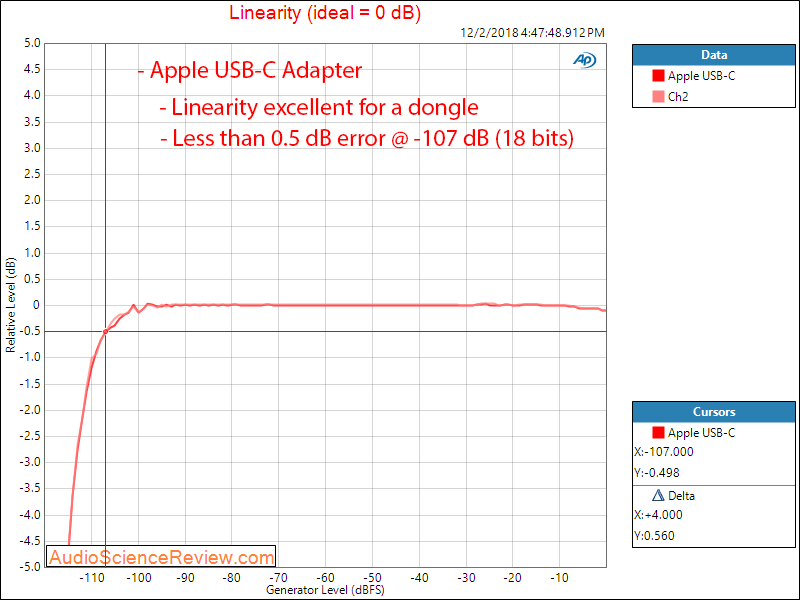

With the apple dongle it seems to manifest a bit differently.

With the apple dongle it seems to manifest a bit differently.